AV 127 – Kintex® Ultrascale™

Aperçu du produit

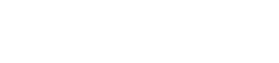

L’AV127 fait partie de notre gamme de solutions de conversion de données et de traitement du signal haute vitesse basées sur la norme VITA 46, VPX.

L’AV127 est entièrement conforme à la norme OpenVPX, prenant en charge divers protocoles de communication tels que PCIe, SRIO, 1 Gbit et XAUI 10 Gbit Ethernet, ainsi que des normes non adoptées par OpenVPX telles que Aurora.

L’AV127 combine jusqu’à 36 interfaces fibre duplex intégral avec une puissance de traitement ultra-élevée fournie par le FPGA Xilinx® Kintex® Ultrascale™, ce qui le rend parfaitement adapté aux applications de traitement du signal embarqué telles que la communication à large bande, le radar à réseau phasé ou les applications de guerre électronique.

L’AV127 dispose de trois synthétiseurs d’horloge à faible gigue entièrement indépendants pour la prise en charge de la plupart des protocoles de communication sur fibre.

L’AV127 comprend un FPGA Xilinx® Kintex® Ultrascale™ KU115 pour une capacité de traitement impressionnante de plus de 7 TMAC (Multiply Accumulate per second), deux mémoires SDRAM DDR3 256M64 haute vitesse pour le traitement des données et deux mémoires FLASH synchrones de 1 Go pour le stockage de plusieurs micrologiciels.

L’AV127 dispose d’une interface USB 2.0 et d’une interface Ethernet 10/100 destinée à être utilisée pour la surveillance et la supervision du système.

L’AV127 est livrée avec des pilotes logiciels complets pour Windows et Linux. Un kit de développement FPGA est fourni, comprenant tous les cœurs nécessaires à la création d’une application FPGA utilisateur.

Avantages clés

- 12, 24 ou 36 interfaces fibre full duplex

- Jusqu'à 14 Gbps par fibre de 0°C à 55°C (version -AS)

- Jusqu'à 10 Gbps par fibre de -40°C à +85°C (versions -AR, -CA et -CR)

- Trois synthétiseurs d'horloge indépendants à faible distorsion

- FPGA AMD Kintex® Ultrascale™ KU115 FPGA programmable par l'utilisateur

- 800 MHz 2x 256M64 DDR3 SDRAM

- Compatiblee au standard 3U OpenVPX

- Versions robustes refroidies par air et par conduction

Specs techniques

Optical Links• 0, 12, 24 or 36 Optical Transceivers

• 850 nm VCSEL array technology • 14 Gbps from 0°C to +55°C (-AS) • Total data throughput up to 1008 Gbps • 10 Gbps from -40°C to +85°C (-AR, -CS, -CR) • Total data throughput up to 720 Gbps • Connectors: MTP (MPO) adapter

|

Memory• Two banks 256M64 DDR3 SDRAM, 800 MHz clock

• Option for two banks 512M64 DDR3 SDRAM, 800 MHz clock, -AS version only • Two 1 Gbit QSPI NOR FLASH memory

|

Software support• Software Drivers:

• Windows 10 • Linux • Application example: • Windows and Linux

|

Optical Links Interfaces

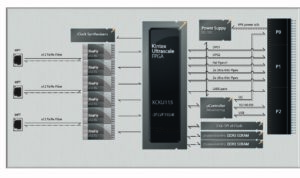

The AV127 supports up to three x12 Optical Links Transmitters and three x12 Optical Links Receivers.The Optical Links Transmitters and Receivers support up to 14 Gbps on commercial temperature grade (0°C to +55°C) and up to 10 Gbps on industrial temperature grade (-40°C to +85°C). The Optical links use a proven 850 nm VCSEL array technology.The AV127 supports three MTP (MPO) adapters on the front panel supporting x24 MT ferules.

Clock Synthesizers

The AV127 provides one low jitter clock synthesizers for each x12 Optical Links transceiver block.Each clock synthesizer can synthesize two clock references for the FPGA GTHs from 60 MHz to 820 MHz locked on a common 25 MHz, allowing support of all major protocols such as Aurora, GigE, PCIe Gen 1 and Gen 2, SATA, SRIO and XAUI 10Gbit Ethernet up to 14 Gbps.

FPGA

The AV127 is fitted with a Xilinx® Kintex® Ultrascale™ KU115 user programmable FPGA. Only few resources are used to control and communicate with external hardware such as DDR3 SDRAM and monitoring sub-system, leaving most of the logic and block RAM and all DSP resources available for customer processing.Dedicated to signal processing, the Xilinx Kintex Ultrascale KU115 FPGA includes 1,451 K logics cells, 2,160 36 Kbit RAM blocs, 6 PCIe interface blocs and 5,520 DSP48 slices for an impressive processing power of more than 7 TMACs.The FPGA is delivered in -2 speed grade.

Memories

The AV127 includes two 800 MHz 256M64 DDR3 SDRAM memory banks and two 1 Gbit QSPI FLASH used to store multiple FPGA configuration files.A dual banks 512M64 is available on demand for -AS only version

VPX interface

The AV127 features an OpenVPX VITA 65 compliant interface with support for two Fat Pipes for Data Plane, one Fat Pipe for Expansion Plane, two Ultra-Thin Pipes for Control Plane and two User Defined Ultra-Thin Pipes on P1. The AV127 also supports 28 LVCMOS33 signals and 4 SUB-LVDS differential pairs on P2 plus USB2.0 and 10/100 Ethernet for supervision and monitoring.The AV127 features two low phase noise clock generators able to synthesize clock references for the FPGA GTHs from 60 MHz to 820 MHz, allowing support of all major protocols such as Aurora, GigE, PCIe Gen 1, 2 and 3, SATA, SRIO and XAUI 10Gbit Ethernet up to 16.375 Gbps.

Microcontroller

The AV127 features a 32-bit 80 MHz microcontroller used primarily for board monitoring and supervision.The microcontroller supports a USB 2.0 and a 10/100 Ethernet interfaces accessible on the VPX P2 user IO pins through an ApisSys AR102 Rear Transition Module or an ANSI/VITA 46.10 compliant custom RTM board.The microcontroller firmware includes all necessary features for board monitoring and supervision.

Firmware

The AV127 comes with a firmware package which includes VHDL cores allowing for control and communication with all AV127 hardware resources.A base design is provided which demonstrates the use of the AV127 and gives users a starting point for firmware development. The AV127 firmware package is supported on the Xilinx VIVADO® 2017.4 design suite and later.

Software

The AV127 is delivered with software drivers for Windows 10 and Linux.

Ruggedization

The AV127 is delivered in air cooled and conduction cooled standard or rugged versions for use in severe environmental conditions.Standard VITA 47 supported ruggedization levels are EAC4, EAC6, ECC3 and ECC4.

Livrables

| Part Number | A | V | 127 | - | rr | - | a | b | |

|---|---|---|---|---|---|---|---|---|---|

| Ruggedization level | Air Standard Air Rugged Conduction Standard Conduction Rugged |

- - - - |

- - - - |

- - - - |

- - - - |

AS AR CS CR |

- - - - |

- - - - |

- - - - |

| Options 1 | FPGA Kintex Ultrascale KU115 | - | - | - | - | - | - | 1 | - |

| Options 2 | No Optical Links 12 Optical Links 24 Optical Links 36 Optical Links |

- - - - |

- - - - |

- - - - |

- - - - |

- - - - |

- - - - |

- - - - |

0 1 2 3 |

Ruggedization

| Air flow, Standard AS (VITA 47 EAC4 |

Air flow, Rugged AR (VITA 47 EAC6) |

Conduction Standard CS (VITA 47 ECC3) |

Conduction Rugged CR (VITA47 ECC4) |

|

|---|---|---|---|---|

| Operating Temperature |

0°C to +55°C (1) (8 CFM airfl ow at sea level) |

-40 to +70ºC (1) (8 CFM airfl ow at sea level) |

-40°C to +70°C (Card Edge) |

-40°C to +85°C (Card Edge) |

| Non Operating Temperature | -40°C to +85°C | -50°C to +100°C | -50°C to +100°C | -55°C to +105°C |

| Operating Vibration (Random) |

5Hz - 100Hz +3 dB/octave 100Hz-1kHz = 0.04 g2/Hz 1kHz - 2kHz -6 dB/octave |

5Hz - 100Hz +3 dB/octave 100Hz - 1kHz = 0.04 g2/Hz 1kHz - 2kHz -6 dB/octave |

5Hz - 100Hz +3 dB/octave 100Hz - 1kHz = 0.1 g2/Hz 1kHz - 2kHz -6 dB/octave |

5Hz - 100Hz +3 dB/octave 100Hz - 1kHz = 0.1 g2/Hz 1kHz - 2kHz -6 dB/octave |

| Operating Shock | 20g, 11 millisecond, half-sine | 20g, 11 millisecond, half-sine | 40g, 11 millisecond, half-sine | 40g, 11 millisecond, half-sine |

| Operating Relative Humidity |

0% to 95% non-condensing |

0% to 95% non-condensing |

0% to 95% non-condensing |

0% to 95% non-condensing |

| Operating Altitude |

@ 0 to 10,000 ft with adequate airflow |

@ 0 to 30,000 ft with adequate airflow |

@ 0 to 30,000 ft | @ 0 to 60,000 ft |

| Conformal Coating | No | Optional (default acrylic 1B31) | Yes (default acrylic 1B31) | Yes (default acrylic 1B31) |

Applications

- EW SDR-COMINT

- Radar Emitter-Receiver

- Physics

- EW ESM-RWR

- Data Communication