-contenu en anglais-

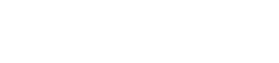

reflex ces has developed a demonstration based on the JESD204B standard, available for the Achilles Arria® 10 SoC module. A reference design is also available.

The JESD204B is a standardized serial interface between data converters (ADCs and DACs) and logic devices (FPGAs or ASICs), with serial data rates up to 12.5 Gbps.

Often used for high speed data conversion connected to FPGA, is it a very flexible solution.

The DAC and the ADC both offers 4 lanes @ 5 Gbps with sampling frequency of 500MHz.

Some FPGA resources (HPS included) :

- LUT: 31K

- M20K: 608 (29%)

- IOPLL: 5 (45%)

Featuring an ARM dual-core Cortex-A9 MPCore and up to 660KLEs of advanced low-power FPGA logic elements, the Arria® 10 SoC SoM combines the flexibility and ease of programming of a CPU with the configurability and parallel processing power of an FPGA.

With its four standardized FMC interfaces, it gives users a unique, flexible, and high-end solution for faster project completion. Featuring the largest density FPGA-SoC device, excellent signal integrity, an unequaled number of IOs and features, developers really do benefit from the best in class design experience.

A Development Kit with the Starter Carrier board, or with a PCIe carrier board is available separately to quickly start FPGA and software development. The SoM can be purchased separately for production systems, in three different versions: Lite 12G, Indus and Indus 12G.

The BSP is available upon request for this JESD204B demonstration. Contact sales@reflexces.com for more information.