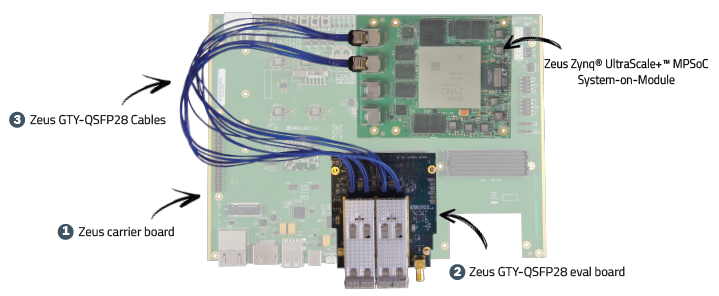

PARIS – reflex ces, a leading European-based provider of custom embedded systems and High-End FPGA COTS boards, has developed a 100G Ethernet MAC HDL test design, based on the Zeus Zynq® UltraScale+™ MPSoC system-on-module, and designed for high performance applications.

This test design is allowing the implementation of one up to three 100G ethernet links, depending on the FPGA matrix chosen, through GTY-QSFP28 connectors.

The main benefit of this test design is to plug in high-speed interfaces.

This test design was developed using AMD’s 100G Ethernet Subsystem.

The Zeus Zynq® UltraScale+™ MPSoC is a System-on-Module, available in two different versions: based on the AMD ZU11EG FPGA, or based on the AMD ZU19EG FPGA.

Using FPGA version ZU11EG: 2x 100G links available

Using FPGA version ZU19EG: potentially up to 3x 100G links available

The Zeus System-on-Module offers a PCIe Gen2 x4 Root Complex, a PCIe Gen3 x16 End Point, but also a Quad-Core ARM Cortex-A53. With a total of 304 SE IOs (96 LVDS), 16 GTY @25.78Gbps (Top side), 32 GTH @12.5Gbps (Bot side) and 3x DDR4 banks (16GByte Total), this module has been developed to perfectly fit high-performance needs.

This design runs on reflex ces’ Zeus module and carrier board, and uses the Zeus GTY-QSFP28 evaluation board to loop back during testing. It’s a starter so that customers can run the design with their own carrier board and installation, if necessary, reusing IP, interfaces, pinout… according to their needs.

The test design is available upon request. Contact sales@reflexces.com for more information.